| Tweet | پ@ |

http://techon.nikkeibp.co.jp/article/NEWS/20070211/127607/

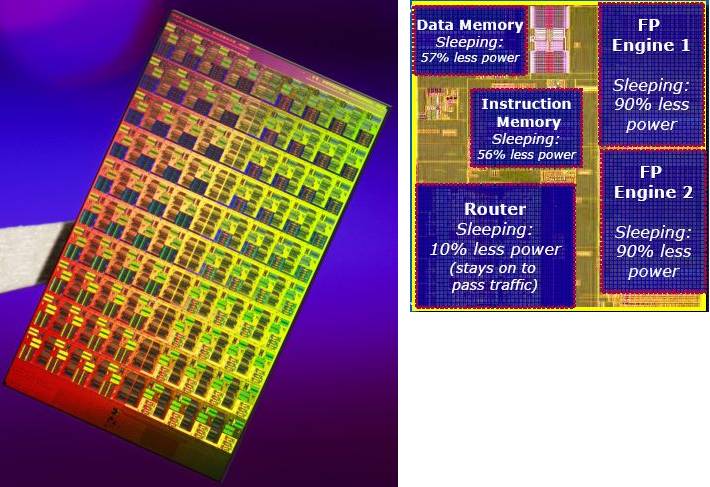

ƒ^ƒCƒ‹1Œآ‚ً21‚ج“d—حٹا—‚ج‹و‰و‚ة•ھٹ„پBژتگ^‚إ‚ح‚»‚ج‚¤‚؟‚ج5‹و‰و‚ئƒXƒٹپ[ƒvژ‚ج“d—حچيŒ¸Œّ‰ت‚ًژ¦‚µ‚ؤ‚¢‚éپB

پ@•ؤIntel Corp.‚ح2007”N2Œژ11“ْپC”¼“±‘ج‹Zڈp‚جچ‘چغٹw‰ïپuIntegrated Solid State Circuits Conference پiISSCCپj2007پvپi2007”N2Œژ11پ`15“ْپC•ؤچ‘ƒTƒ“ƒtƒ‰ƒ“ƒVƒXƒRژsپj‚جٹJچأ‚ةچ‡‚ي‚¹‚ؤپC80Œآ‚جCPUƒRƒA‚ً1ƒ`ƒbƒvڈم‚ةڈWگد‚µ‚½ƒ}ƒCƒNƒچƒvƒچƒZƒT‚جژژچىƒ`ƒbƒv‚جگ«”\‚ج‚¢‚‚آ‚©‚ً”•\‚µ‚½پB“¯ژذ‚ھ2006”N9Œژ‚جپuIntel Developer ForumپiIDFپjFall 2006پv‚إڈ‰ŒِٹJ‚µ‚½“¯ƒ`ƒbƒv‚جڈء”ï“d—ح‚âگفŒv‚جڈعچׂً–¾‚ç‚©‚ة‚µ‚½‚à‚جپiٹضکA‹Lژ–پjپB

پ@‹ï‘ج“I‚ة‚حپC“dŒ¹“dˆ³0.95VپC“®چىژü”gگ”3.16GHz‚جڈêچ‡‚ة‰‰ژZگ«”\‚ح1.01TFLOPSپCڈء”ï“d—ح‚ح62W‚إ‚ ‚é‚ئ‚¢‚¤پBŒ»چف‚جƒfƒ…ƒAƒ‹پEƒRƒAŒ^86Œnƒ}ƒCƒNƒچƒvƒچƒZƒT‚ھڈء”ï“d—ح60پ`100W‚إ10Gپ`20GFLOPS‚إ‚ ‚邱‚ئ‚©‚çپCچ،‰ٌ‚جƒ`ƒbƒv‚ح’Pˆتڈء”ï“d—ح“–‚½‚è‚ج‰‰ژZگ«”\‚ح50”{ˆبڈم‚ة‚ب‚éپB“Œ‹‘هٹw‚ئچ‘—§“V•¶‘ن‚ھ2006”N11Œژ‚ة”•\‚µ‚½ƒvƒچƒOƒ‰ƒ€‰آ”\‚بƒAƒNƒZƒ‰ƒŒپ[ƒ^LSIپuGRAPE-DRپv‚جپC60W‚إ 512GFLOPS‚ئ”نٹr‚µ‚ؤ‚à–ٌ2”{پC“d—حŒّ—¦‚ھچ‚‚¢پB

پ@چ،‰ٌ‚جƒ}ƒCƒNƒچƒvƒچƒZƒT‚حƒ`ƒbƒv‘S‘ج‚إ1‰Œآ‚جƒgƒ‰ƒ“ƒWƒXƒ^‚ھڈWگد‚³‚ê‚ؤ‚¢‚éپBƒ`ƒbƒv‚حپuƒ^ƒCƒ‹پv‚ئŒؤ‚ش80Œآ‚ج‹و‰و‚ة•ھ‚©‚ê‚éپBƒ^ƒCƒ‹1Œآ’†‚ة‚ح•‚“®ڈ¬گ”“_‰‰ژZƒ†ƒjƒbƒg2Œآ‚ئپuƒ‹پ[ƒ^پ[پv‚ئŒؤ‚شƒXƒCƒbƒ`‰ٌکHپC‚¨‚و‚رƒfپ[ƒ^—pƒپƒ‚ƒٹ‚ئ–½—كƒZƒbƒg—pƒپƒ‚ƒٹ‚ب‚ا‚ھ“‹چع‚³‚ê‚ؤ‚¢‚éپBƒ‹پ[ƒ^پ[‚حپC—×گع‚·‚é 4Œآ‚جƒ^ƒCƒ‹‚ئ‚جگع‘±—p‚ة4ŒآپC‚³‚ç‚ةƒRƒA‚ة’£‚èچ‡‚ي‚¹‚éپu3Dگد‘wƒپƒ‚ƒٹپvپiIntelژذپj‚ئŒؤ‚شSRAM‚ًگع‘±‚·‚邽‚ك‚ج1Œآ‚جŒv5Œآ‚ج“üڈo—حƒ|پ[ƒg‚ً”ُ‚¦پC‘چƒfپ[ƒ^“]‘——e—ت‚ح80Gƒrƒbƒg/•b‚إ‚ ‚éپB‚ب‚¨پC3Dگد‘wƒپƒ‚ƒٹ‚جڈعچׂة‚آ‚¢‚ؤ‚حگG‚ê‚ؤ‚¢‚ب‚¢پB

پ@

پ@ڈء”ï“d—ح‚جŒّ—¦‚ً‘ه‚«‚چ‚‚ك‚邱‚ئ‚ة‚آ‚ب‚ھ‚ء‚½‹Zڈp‚ئ‚µ‚ؤIntelژذ‚حپuFine Grain Power Managementپv‹Zڈp‚ً‚ ‚°‚éپB‚±‚ê‚حپCٹeƒ^ƒCƒ‹‚ً‚»‚ꂼ‚ê21‚ج“d—حٹا—‚ج‹و‰و‚ة•ھ‚¯پC“d—ح‚ً‹و‰و‚²‚ئ‚ةگ§Œن‚·‚é‹Zڈp‚إ‚ ‚éپB

پ@“¯ژذ‚حپCچ،‰ٌ‚جƒ`ƒbƒv‚إ5.7GHz‚ة‚ـ‚إ“®چىژü”gگ”‚ًچ‚‚ك‚½ڈêچ‡‚جگ«”\‚à”•\‚µ‚½پB‚»‚جڈêچ‡‚ج“dŒ¹“dˆ³‚ح1.35VپC‰‰ژZگ«”\‚ح1.81TFLOPS‚ئ”ٌڈي‚ةچ‚‚¢‚ھپCڈء”ï“d—ح‚ح265W‚ئ3.16GHz“®چى‚جژ‚ج4”{’´‚ة‚ب‚ء‚ؤ‚µ‚ـ‚¤‚ئ‚¢‚¤پB

پ@‚³‚ç‚ة‹Zڈp“I‚بڈعچׂحپC2Œژ12“ْپiŒ»’nژٹشپj‚ةISSCC 2007‚إ•ٌچگ‚·‚é‚ئ‚¢‚¤پB

|

|

پ£‚±‚جƒyپ[ƒW‚ج‚s‚n‚o‚ض HOME > ƒeƒXƒg12Œfژ¦”آ

|

|

“ٹچeƒRƒپƒ“ƒg‘SƒچƒO پ@ƒRƒپƒ“ƒg‘¦ژ”zگM پ@ƒXƒŒŒڑ‚ؤˆث—ٹ پ@چيڈœƒRƒپƒ“ƒgٹm”F•û–@

|

|

پ@‘è–¼‚ة‚ح•K‚¸پuˆ¢ڈC—…‚³‚ٌ‚ضپv‚ئ‹Lڈq‚µ‚ؤ‚‚¾‚³‚¢پB

پ@‘è–¼‚ة‚ح•K‚¸پuˆ¢ڈC—…‚³‚ٌ‚ضپv‚ئ‹Lڈq‚µ‚ؤ‚‚¾‚³‚¢پB

Œfژ¦”آ,‚l‚k‚ًٹـ‚ق‚±‚جƒTƒCƒg‚·‚ׂؤ‚ج

ˆêگط‚جˆّ—pپA“]چعپAƒٹƒ“ƒN‚ً‹–‰آ‚¢‚½‚µ‚ـ‚·پBٹm”Fƒپپ[ƒ‹‚ح•s—v‚إ‚·پB

ˆّ—pŒ³ƒٹƒ“ƒN‚ً•\ژ¦‚µ‚ؤ‚‚¾‚³‚¢پB

|

|

|

|

|

|

|

|