http://www.asyura2.com/15/hasan100/msg/650.html

| Tweet |

ジリ貧のインテル、生き残りかけ「謎の」買収 半導体業界、「異端児」台頭で革命的変化

http://biz-journal.jp/2015/09/post_11604.html

2015.09.18 文=湯之上隆/微細加工研究所所長 Business Journal

■なぜインテルはアルテラを買収したか

半導体業界では2015年に入って、大型のM&A(合併・買収)が相次いでいる。そのなかでも米インテルがFPGAメーカーの米アルテラを買収したことが、ずっと気にかかっていた。FPGAとはField Programmable Gate Arrayの略で、チップを製造した後にプログラムが可能な半導体デバイスであり、米ザイリンクスと並んでアルテラが世界の2強である。

インテルは、PC用プロセッサがジリ貧、スマートフォン(スマホ)用プロセッサは大赤字、データセンタ用プロセッサが唯一、稼ぎ頭で基幹事業となっている。ところが、2014年に米マイクロソフトが検索エンジンBingの高速処理のためにFPGAを導入するなど、データセンタ用プロセッサとしてFPGAが急浮上してきた。

インテルのプロセッサとFPGAで電力当たりの性能を比較した場合、検索処理では約10倍、複雑な金融モデルの解析では実に約25倍もFPGAのほうが高いという。このままいくと頼みの綱であるデータセンタ事業も失う可能性があり、インテルとしては生き残りのためになんとしてもアルテラを買収しなくてはならなかったのである。

しかし、なぜFPGAはインテルのCPUより電力当たりの性能が1桁も優れているのだろうか。そもそも、なぜ単純に処理速度を比較せず、電力当たりの性能を比較するのだろうか。 そして、このような事態が急浮上してきたのはなぜなのか。

これらの疑問を解決するために8月中旬、産業技術総合研究所(産総研)に在籍しているFPGAの専門家に教えを乞うことにした。

■表に出てこなかったFPGA

筆者が訪ねたのは、産総研ナノエレクトロニクス研究部門のエレクトロインフォマティックスグループ長で、10年以上FPGAを研究している小池汎平氏である。

小池氏によれば、FPGAは突然浮上したのではないという。たとえば、マイクロソフトは10年以上も前からFPGA関係の学会で活躍していて、その人脈が検索エンジンBing用のFPGAの開発につながっているし、インテルも随分前からFPGAのベンチャーを買収しようと物色していたらしい。

では、なぜそのような動きが半導体業界に聞こえてこなかったのか。それは、どうやら半導体業界においてFPGAが異端視されていることに原因があるようだ。

たとえば、ISSCCやVLSIシンポジウムのような半導体の国際学会には、FPGAの発表がほとんどない。その理由を小池氏に聞いてみると、プロセッサやメモリなどの専門家が多数を占める半導体の学会は、FPGAの技術への関心が薄かったのではないかとのこと。その結果、FPGA関係者の主流は、ACM(Association for Computing Machinery)などコンピュータやCADソフト技術を中心とした学会に参加するようになっていったという。

実際に、小池氏に見せてもらったのだが、ACMには「FPGA」という名称の専門のシンポジウムや「TRETS」という名称の専門のジャーナル誌まである。このようにFPGA関係者は、まったく異なる学会を中心として研究発表を行っていたため、半導体業界にその動向が十分に伝わってこなかった。それゆえ、FPGAの動向を知らなかった多くの半導体業界人には、FPGAが急浮上してきたように見えたわけだ。

■FPGAは初期開発コスト最小のLSI

FPGAの躍進は、ロジックLSIのASICを置き換えることから始まった。ASICとは、Application Specific Integrated Circuitの略で、特定用途向けにつくられた半導体デバイスである。以下で、FPGAとASICを比較してみよう。(図1)

ASICは、SRAM、CPUなどさまざまなマクロセル(Intellectual Property、IP)を自由自在に使うことができ、設計自由度が高いため、高機能や高集積化に向いている。しかし、開発期間が長く、開発コストも高い。また、設計やプロセスが極度に困難度を増している昨今においては、一度つくってしまったら変更できないため、本当に設計通りに動くのか、当初の納期と予算通りにできるのか、そして本当に売れるのかといったリスクが付きまとう。

一方、FPGAはASICに比べれば設計の自由度は低い。また、ASICに比較して3〜4倍のトランジスタを必要とするため、チップサイズが大きくなり、チップ単価は高い。FPGAは、ザイリンクスの共同設立者であるRoss Freemanが発明したLSIだが、ザイリンクスの最初の製品「XC2064」をレイアウトしたBill Carterは、「なんというトランジスタの無駄使いだろう」と述べたという。

しかし、FPGAは、ASICに比べて開発期間は極めて短く、開発コストも小さい。さらに、再プログラミングが可能という特徴があるので、チップ製造後に容易に機能を変更することができる。小池氏は、FPGAを「ソフトウエアのように開発できるハードウエア」と称している。

ここで、FPGAとASICのチップコスト比較を行ってみよう(図2)。チップコストは、「(開発費+製造費)/生産数量」で産出する。大量生産する場合は、FPGAよりASICのチップコストが安い。規模の経済が働くからである。一方、生産数量が少ない場合は、ASICよりもFPGAのほうがチップコストが安くなる。小池氏は、「FPGAとはもっとも初期コストが安いLSI」であると述べている。

■FPGAがASICを代替する

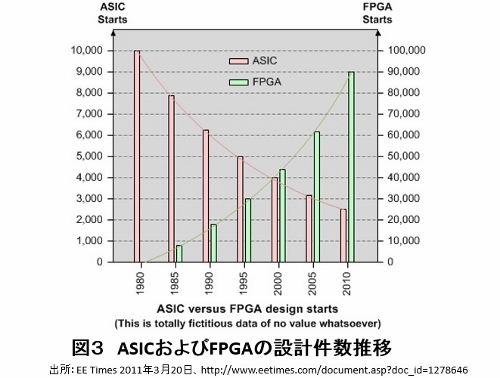

1980年〜2010年までのASICとFPGAの設計件数の推移を見てみよう(図3)。80年に1万件もあったASICの設計件数は急激に減少し、10年には2500件程度になってしまった。一方、それと反比例するようにFPGAの設計件数は急増しており、10年には9万件に達した。

この背景要因には、微細化が進み、マスク開発費およびプロセス開発費が高騰したことがある。また、スマホなどの携帯電話、タブレット、PC、デジタル家電など、ロジックLSIを必要とする製品の種類は増大する反面、製品サイクルは短命化している。それゆえ、ロジックLSIは多品種少量生産を余儀なくされることになった。

その結果、マスク開発費やプロセス開発費が高くリスクも高いASICが敬遠され、これに代わって初期開発コストが最小のFPGAが重宝されるようになったのである。これが、FPGAがASICを代替している理由である。

FPGAが微細化の最先端を走る

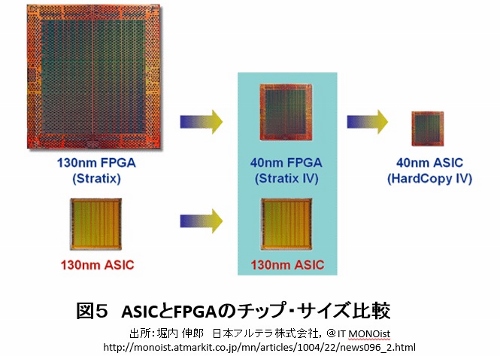

FPGAの問題点のひとつに、ASICと比較して3〜4倍のトランジスタを必要とするということがあった。これは、FPGAのチップサイズが大きくなり、それが高いチップ単価に直結している。ところが、FPGAが微細化の最先端を走るようになったため、この問題も解消されてきた。

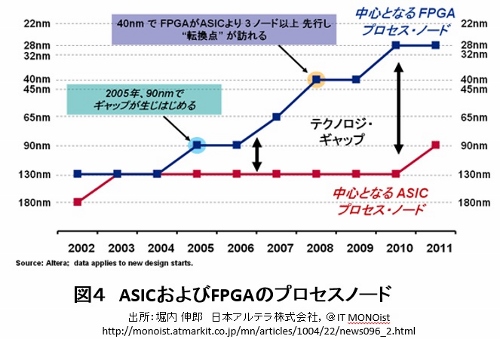

ASICとFPGAの微細化の推移を見てみよう(図4)。02年以前は、ASICのほうがFPGAよりも微細化されていた。ところが、03−04年にFPGAの微細化がASICに追いつくと、それ以降は、FPGAの微細化が先行するようになる。そして、08年以降はFPGAがASICの3世代先の微細化を行うようになる。

その結果、08年時点でみると、ASICは130nm、FPGAは40nmで、チップサイズは同等レベルになり(図5)、FPGAのコストパフォーマンスは著しく向上した。FPGAのチップサイズが大きく、コストパフォーマンスが悪いという問題はかなり解消された。

■演算の燃費でCPUを上回る

ここ数年、IoT(Internet of Things:モノのインターネット)が普及し始め、ビッグデータの活用が本格化し、それに伴ってモバイル端末およびデータセンタが増加している。これらに使われる電力量は増大し、さらにその発熱も問題となっている。つまり、ローパワーの必要性が増している。

このような背景から、例えばデータセンタでは単にコンピュータの処理速度を上げるのではなく、演算におけるエネルギー効率を問題にするようになった。具体的には、演算1回あたりに必要なエネルギーを小さくすることが求められているのである。小池氏によれば、これはいわば「計算アーキテクチャの燃費」のようなものだという。なかなか面白い喩えである)。

図6は、各種LSIにおける32ビット演算1回あたりに必要なエネルギー(ピコジュール/1オペレーション、pJ/op)を、米スタンフォード大学兼NVIDIAチーフサイエンティストのBill Dally教授が2005年のISSCCのパネル討論で見積もった結果をもとに、小池氏がまとめたものである。

インテルのCPUは、ノイマン型といわれ、メモリに格納されている命令を演算回路が逐次実行し、その演算結果をレジスタやメモリに格納するということを、複雑な制御回路を用いて繰り返す。その結果、エネルギー効率は200pJ/opと最も悪い。一定の計算に特化したDSP(今ならGPUもこの分類に入ろう)では、CPUより演算のロスが少ないため、60pJ/opと、CPUの3倍程度のエネルギー効率となる。

ASICでは、制御回路やメモリがなく、演算回路が直接結線されている。データだけが、数百段のパイプラインを流れていくようにできれば、無駄を最小化できる。その結果、単体の演算回路そのものの2pJ/opに近いCPUの百倍のエネルギー効率が実現できるはずである。しかし前述したように、マスクやプロセス開発費が最も高く、プログラマビリティはないため一度つくってしまった後の変更ができず、リスクも高い。

一方、FPGAでは演算回路をプログラムでつなぐ。そのエネルギー効率はASICよりおよそ1桁悪いと考えられるが、20pJ/opで、CPUよりは一桁良い。しかも、製造後に何度でもプログラムを修正できる。

結局、FPGAはCPUよりエネルギー効率が良いこと、ASICに対してはエネルギー効率で1桁劣るがプログラマビリティがあって使いやすく、初期開発コストやリスクを軽減できることなどが決め手となって、現在注目されるに至っている。

■FPGAの今後の展望

コスト、性能、エネルギー効率、使いやすさなどが最先端のデータセンタの要求とマッチしたために、FPGAにスポットライトが当たるようになったといえる。

インテルは、アルテラを買収することによりFPGAの技術を手に入れた。この技術を生かせば、もともと強かったインテルのデータセンタ事業はさらに強化されることになる。また、FPGAはASICを代替し続けていることから、インテルにとって新たなビジネス分野に進出することも可能だ。インテルは「良い買い物」をしたといえよう。

さらに、スーパーコンピュータについてはトップ10機種までのプロセッサをNVIDIAのGPUが占めているが、この分野にもFPGAが進出する可能性がある。小池氏によれば、10年ほど前に、スパコン用のアクセラレータとしてGPUとともにFPGAが検討されていたこともあり、性能的にはどっこいどっこいとの評価結果だったそうだ。

その際に問題となったのは、FPGAのプログラミングに多大な時間がかかるということだったらしい。もしこれが解決できれば、スパコン用のプロセッサとしても、FPGAが使われるかもしれない。

半導体の国際学会では異端児扱いされてきたFPGAが、一躍脚光を浴びている。FPGAの時代が到来したといえよう。

(文=湯之上隆/微細加工研究所所長)

|

|

|

|

投稿コメント全ログ コメント即時配信 スレ建て依頼 削除コメント確認方法

▲上へ ★阿修羅♪ > 経世済民100掲示板 次へ 前へ

|

|

スパムメールの中から見つけ出すためにメールのタイトルには必ず「阿修羅さんへ」と記述してください。

スパムメールの中から見つけ出すためにメールのタイトルには必ず「阿修羅さんへ」と記述してください。すべてのページの引用、転載、リンクを許可します。確認メールは不要です。引用元リンクを表示してください。